### ELT 217; Experiment AD-5: Flip-Flops

EQUIPMENT NEEDED: Analog Discovery Computer with Waveform program 7400, quad 2-input NAND 7473, JK M-S Flip-flop

Notes:

- Before wiring each circuit you must have a neat logic diagram showing pin numbers used and functional interconnections. (All circuit diagrams must be included in your report.) When actually assembling the circuit make sure you are using the proper IC. Also do not forget to hook up power and ground to each IC you use and indicate pin numbers for this.

- For ease of typing, negation is sometimes indicated by an asterisk, apostrophe or tilde. Thus X is the same as X\*, which is the same as X', and which is the same as ~X; which are all ways of writing not X (or active low X).

### A. The $\overline{S}-\overline{R}$ Latch

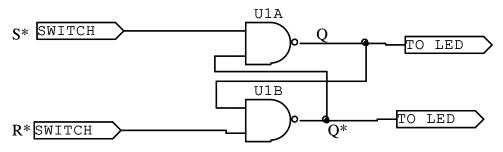

Connect two sections of a 7400 2-input NAND gate as shown in figure 1, below, using two of the virtual data switches as inputs and two of the virtual LEDs as output indicators.

Figure 1, S\*-R\* Latch

- (1) Set inputs  $S^*=1$  and  $R^*=1$  (high). Record the state of the outputs.

- (2) Momentarily bring the S\* input to 0 for a brief time (switch its data switch to 0 and set it back to 1 again). Record the state of the outputs after you pulse the inputs like this.

- (3) Leaving the S\* input high, momentarily bring the R\* input to 0 for a brief time (switch its data switch to 0 and set it back to 1 again). Record the state of the outputs after you pulse the inputs like this.

- (4) Put both input switches into the 0 (low) position and leave them there. Record the state of the outputs; is this a valid condition or not? Explain why in your report.

- (5) First return  $S^*$  to 1 and then  $R^*$  to 1. Record the state of the outputs.

- (6) Again set S\*=0 and R\*=0. Then first return R\* to 1, and then S\* to 1. Record the state of the outputs

**Experiment AD-5**

(7) From the results of this section complete the truth table for the S\*-R\* Latch. A suggested format is shown in figure 2, below

| INP | UTS | OUT | PUTS |          |

|-----|-----|-----|------|----------|

| R*  | S*  | Q   | Q*   | Comments |

| 0   | 0   |     |      |          |

| 0   | 1   |     |      |          |

| 1   | 0   |     |      |          |

| 1   | 1   |     |      |          |

### B. Gated S-R Latch.

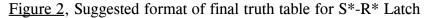

Construct a gated latch using 4 sections of the 7400 chip as shown in figure 3, below.

Figure 3, Gated R-S Latch

Develop the truth table for this latch by doing the following steps in sequence, recording the state of the outputs for each step. (Start with the gate input G=0, which should disable all inputs.)

- (1) Set R=1, S=1; leave G=0

- (2) Set R=1, S=0; leave G=0

- (3) Set R=0, S=0; leave G=0

- (4) Set R=0, S=1; leave G=0

Note: in steps 1-4 the latch should have remained in the same state. Explain why in your report. Was the particular state you observed the same for all groups in the lab? (Check with other students.) Explain why in your report.

(5) Set the gate input G=1, which should enable all inputs

Set

$$S=1$$

,  $R=0$ ; leave  $G=1$

- (6) Set S=0, R=0; leave G=1

- (7) Set S=0, R=1; leave G=1

- (8) with G=1, Set S=1, R=1; then set G=0 record the outputs for each state of G

In your report explain the operation of the latch for step 8.

In your report complete the truth table for the Gated S-R latch. A suggested format is shown in figure 4, below.

| INPUTS |   | OUTPUTS |   |    |          |

|--------|---|---------|---|----|----------|

| G      | R | S       | Q | Q* | Comments |

| 0      | 0 | 0       |   |    |          |

| 0      | 0 | 1       |   |    |          |

| 0      | 1 | 0       |   |    |          |

| 0      | 1 | 1       |   |    |          |

| 1      | 0 | 0       |   |    |          |

| 1      | 0 | 1       |   |    |          |

| 1      | 1 | 0       |   |    |          |

| 1      | 1 | 1       |   |    |          |

Figure 4, Suggested format of final truth table for Gated S-R Latch.

### C. JK Master-Slave (M-S) Flip Flop, 7473.

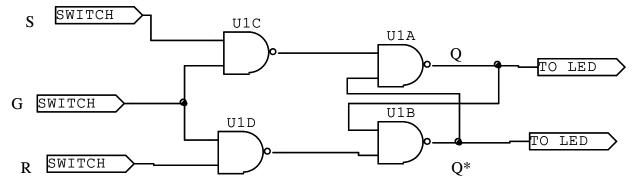

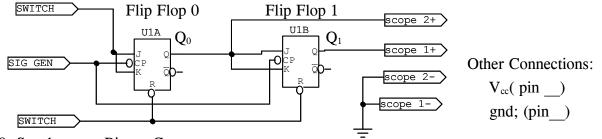

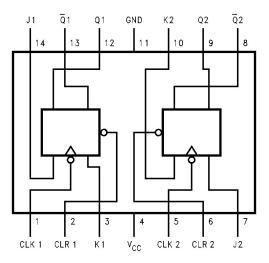

(1) Wire the 7473 as shown in figure 5 using virtual switches and virtual LEDs and a virtual push button output (BUTTON: 0 to 1) on the Analog Discovery as the clock input. Do not forget to hook up, and indicate on your diagram, 5V power and ground (note they are NOT pins 7 and 14).

Figure 5, Connections to 7473

- (2) Verify the synchronous (clocked) truth table for the 7473 (see data sheet) as well as verifying that no change will occur on the outputs, even if the inputs are changed, unless the complete clock signal is present (a transition from low-to-high and back to low). Record the state of the outputs clearly in truth table format similar to the table in the data sheet.

- (3) Verify the asynchronous operation of the 7473 by bring the direct clear (or reset) input low.Verify that it will remain reset, with the clear input overriding all possible conditions at J, K, & CK. Record how you did this.

#### **Experiment AD-5**

### D. Interconnected Flip-Flops; Dynamic Operation -- Asynchronus

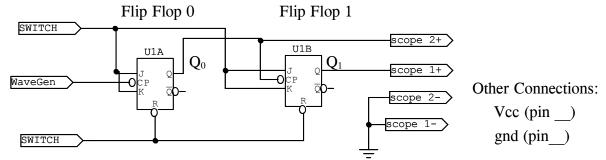

(1) Interconnect the two halves of the 7473 as shown in figure 6, below.

(2) Set the virtual data switches so that the clear input is HIGH and the J and K inputs are also high. Use the Analog Discovery WaveGen to provide a positive 0 to 5V square wave of 100KHz frequency to the clock input instead of a push button. Be sure to reset the default settings of this virtual instrument. You need a peak-to-peak amplitude of 5V, so set the amplitude (which is peak) to be 2.5V. Set the offset to +2.5V so the signal will be 0 to 5V.

Take a "screen shot" of the set-up of the static I/O and the WaveGen and include it in your report. In your report be sure you clearly indicate the meaning of each relevant switch and LED either by labeling the I/O in the Analog Discovery or by indicating the static I/O numbers on your wiring diagram.

(3) Put the Q<sub>0</sub> and Q<sub>1</sub> outputs into the two signal inputs 2+ and 1+ of the Analog Discovery virtual 'scope and trigger the 'scope on the negative-going transition of the Q<sub>1</sub> output of flip-flop 1. Set a trigger level well into the expected amplitude of the outputs, you can try +1V. Offset the two traces so that the Q<sub>1</sub> output is on the top half of the screen and the Q<sub>0</sub> on the bottom.

Run the set-up and observe the waveforms on the 'scope. Take a screen shot of the 'scope (preferred) or draw the timing diagram showing these waveforms for at least 8 clock cycles (adjust the sec/div setting for this). Include this timing diagram in your report – it is part of your data for this section. In your report state the frequency of the  $Q_0$  and  $Q_1$  outputs and the value of the input frequency. What is the ratio of the input frequency to each of the outputs?

- (4) Set the clear input LOW and continue to observe and record the outputs. What effect did this have on the operation of the counter?

- (5) Set the clear input back to HIGH, then set the J and K inputs LOW and continue to observe and record the outputs. What effect did this have on the operation of the counter?

- (6) In your report, for each of the counters in D, E, and F, starting with the counter state  $Q_1=1$ ,  $Q_2=1$ , list the consecutive counter states for at least the next 7 clock pulses. Note that a table

| Pulse | $Q_1$ | $\mathbf{Q}_0$ |

|-------|-------|----------------|

| 0     | 1     | 1              |

| 1     |       |                |

| 2     |       |                |

| 3     |       |                |

| 4     |       |                |

| 5     |       |                |

| 6     |       |                |

| 7     |       |                |

| 8     |       |                |

such as shown in figure 7, listing consecutive states, is called a "State-Table." Comment on the type of the counter for each state-table you make up, *eg*: what modulo, up or down, etc.

#### Figure 7, Sample State-Table

(7) Before disconnecting the counter, have the instructor look at your set-up and sign your data sheet or wiring diagram.

#### **E. Truncated count:**

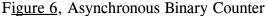

(1) Before disconnecting your asynchronous counter add a decoder to the circuit so it is a modulo 3 instead of modulo 4 counter. One way of doing the is a simple NAND gate with the inputs connected to  $Q_1$  and  $Q_0$  and the output connected to both R\* inputs of the 7473 instead of the switch. See figure 8, below.

Figure 8, Suggested Truncated Asynchronous Binary Counter

Repeat steps (2). (3). (6), and (7) from part D, above.

### **Experiment AD-5**

# F. Interconnected Flip-Flops; Dynamic Operation -- Synchronous

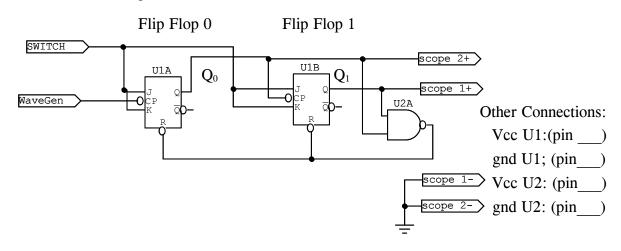

(1) Construct the circuit shown in figure 9, on next page. This is a synchronous binary counter because the clocks in all the circuits receive their signals simultaneously.

Repeat steps (2) through (7) from part D, above.

Figure 9, Synchronous Binary Counter

11/27/17-dw

September 1986 Revised February 2000

# DM7473 Dual Master-Slave J-K Flip-Flops with Clear and Complementary Outputs

# **General Description**

=AIRCHILE

SEMICONDUCTOR

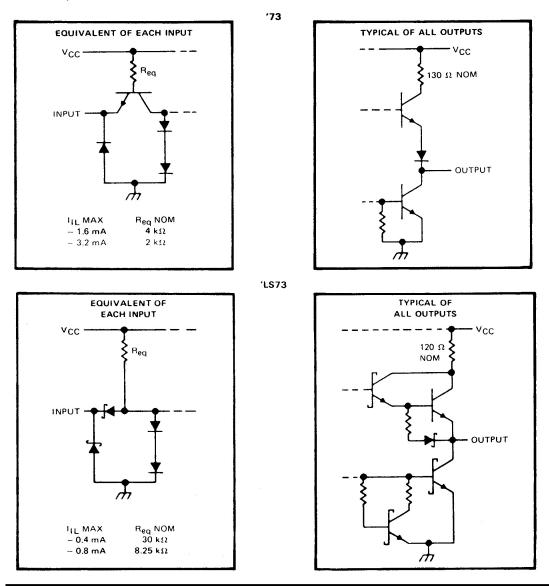

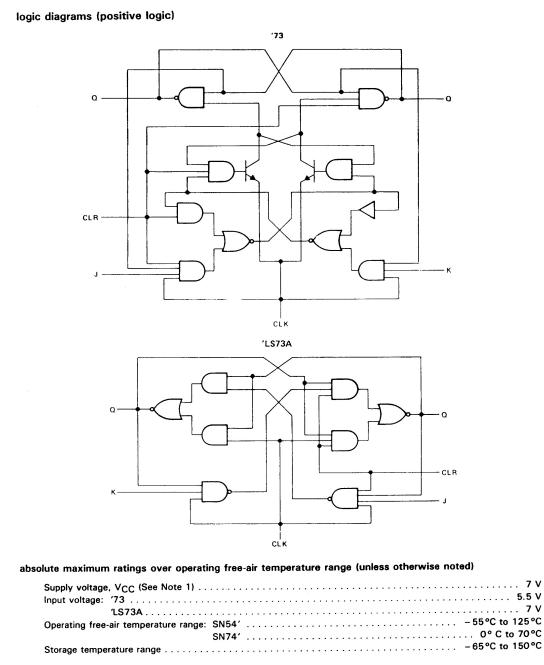

This device contains two independent positive pulse triggered J-K flip-flops with complementary outputs. The J and K data is processed by the flip-flops after a complete clock pulse. While the clock is LOW the slave is isolated from the master. On the positive transition of the clock, the data from the J and K inputs is transferred to the master. While the clock is HIGH the J and K inputs are disabled. On the negative transition of the clock, the data from the master is transferred to the slave. The logic states of the J and K inputs must not be allowed to change while the clock is HIGH. Data transfers to the outputs on the falling edge of the clock pulse. A LOW logic level on the clear input will reset the outputs regardless of the logic states of the other inputs.

# **Ordering Code:**

| Order Number | Package Number | Package Description                                                   |

|--------------|----------------|-----------------------------------------------------------------------|

| DM7473N      | N14A           | 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide |

# **Connection Diagram**

# **Function Table**

| <mark>.к ј</mark> | к<br>х     | Q                       | Q                  |

|-------------------|------------|-------------------------|--------------------|

| ( X               | X          | 1                       |                    |

|                   |            | _ L                     | Н                  |

| ι   L             | L          | Q <sub>0</sub>          | $\overline{Q}_{0}$ |

| τ   H             | L          | н                       | L                  |

| ι   L             | н          | L                       | н                  |

| ъ Н               | н          |                         | Toggle             |

|                   | ւ L<br>ւ H | ι Η Ι<br>ι Ι Η<br>ι Η Η | ι H L H<br>ι L H L |

H = HIGH Logic Leve L = LOW Logic Level

X = Either LOW or HIGH Logic Level

→ = Positive pulse data. the J and K inputs must be held constant while the clock is HIGH. Data is transferred to the outputs on the falling edge of the clock pulse.

$Q_0 =$  The output logic level before the indicated input conditions were established.

Toggle = Each output changes to the complement of its previous level on each HIGH level clock pulse.

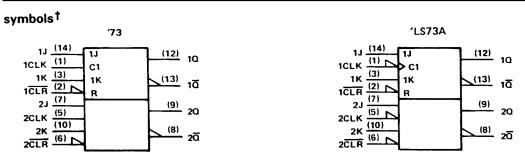

### 73, SN54LS73A, SN7473, SN74LS73A \_ J-K FLIP-FLOPS WITH CLEAR

- DECEMBER 1983 - REVISED MARCH 1988

symbols are in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12.

#### natics of inputs and outputs

# Absolute Maximum Ratings(Note 1)

| Supply Voltage                       | 7V              |

|--------------------------------------|-----------------|

| Input Voltage                        | 5.5V            |

| Operating Free Air Temperature Range | 0°C to +70°C    |

| Storage Temperature Range            | -65°C to +150°C |

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

# **Recommended Operating Conditions**

| Symbol          | Parameter                         |            | Min  | Nom | Max  | Units |

|-----------------|-----------------------------------|------------|------|-----|------|-------|

| V <sub>CC</sub> | Supply Voltage                    |            | 4.75 | 5   | 5.25 | V     |

| V <sub>IH</sub> | HIGH Level Input Voltage          |            | 2    |     |      | V     |

| V <sub>IL</sub> | LOW Level Input Voltage           |            |      |     | 0.8  | V     |

| ОН              | HIGH Level Output Current         |            |      |     | -0.4 | mA    |

| OL              | LOW Level Output Current          |            |      |     | 16   | mA    |

| СLК             | Clock Frequency (Note 3)          |            | 0    |     | 15   | MHz   |

| W               | Pulse Width                       | Clock HIGH | 20   |     |      |       |

|                 | (Note 3)                          | Clock LOW  | 47   |     |      | ns    |

|                 |                                   | Clear LOW  | 25   |     |      | 1     |

| SU              | Input Setup Time (Note 2)(Note 3) |            | 01   |     |      | ns    |

| Н               | Input Hold Time (Note 2)(Note 3)  |            | 0↓   |     |      | ns    |

| T <sub>A</sub>  | Free Air Operating Temperature    |            | 0    |     | 70   | °C    |

Note 2: The symbol ( $\uparrow$ ,  $\downarrow$ ) indicates the edge of the clock pulse is used for reference: ( $\uparrow$ ) for rising edge, ( $\downarrow$ ) for falling edge.

Note 3:  $T_{A}$  = 25°C and V  $_{CC}$  = 5V.

# **Electrical Characteristics**

over recommended operating free air temperature range (unless otherwise noted)

| Symbol          | Parameter                         | Conditions                                     |       | Min | Typ (Note 4) | Max  | Units |

|-----------------|-----------------------------------|------------------------------------------------|-------|-----|--------------|------|-------|

| V <sub>I</sub>  | Input Clamp Voltage               | V <sub>CC</sub> = Min, I <sub>I</sub> = -12 mA |       |     |              | -1.5 | V     |

| V <sub>OH</sub> | HIGH Level                        | V <sub>CC</sub> = Min, I <sub>OH</sub> = Max   |       | 2.4 | 3,4          |      | V     |

|                 | Output Voltage                    | V <sub>IL</sub> = Max, V <sub>IH</sub> = Min   |       | 2.4 | 5.4          |      | Ý     |

| V <sub>OL</sub> | LOW Level                         | V <sub>CC</sub> = Min, I <sub>OL</sub> = Max   |       |     | 0.2          | 0.4  | V     |

|                 | Output Voltage                    | V <sub>IH</sub> = Min, V <sub>IL</sub> = Max   |       |     | 0.2          | 0.4  | · · · |

| I <sub>I</sub>  | Input Current @ Max Input Voltage | V <sub>CC</sub> = Max, V <sub>I</sub> = 5.5V   |       |     |              | 1    | mA    |

| IIH             | HIGH Level                        | V <sub>CC</sub> = Max                          | J, K  |     |              | 40   |       |

|                 | Input Current                     | $V_{I} = 2.4 V$                                | Clock |     |              | 80   | μΑ    |

|                 |                                   |                                                | Clear |     |              | 80   |       |

| ۱ <sub>۱۲</sub> | LOW Level Input                   | V <sub>CC</sub> = Max J, K                     |       |     | -1.6         |      |       |

| Current         | Current                           | $V_{I} = 0.4 V$                                | Clock |     |              | -3.2 | mA    |

|                 |                                   |                                                | Clear |     |              | -3.2 | 1     |

| los             | Short Circuit Output Current      | V <sub>CC</sub> = Max (Note 5)                 | •     | -18 |              | -55  | mA    |

| Icc             | Supply Current                    | V <sub>CC</sub> = Max, (Note 6)                |       |     | 18           | 34   | mA    |

|                 |                                   |                                                |       |     |              |      |       |

Note 4: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 5: Not more than one output should be shorted at a time.

Note 6: With all outputs OPEN, I C is measured with the Q and Q outputs HIGH in turn. At the time of measurement the clock input grounded.

# Switching Characteristics at $V_{CC}=5V$ and $T_{A}=25^{\circ}C$

| Symbol           | Parameter                                       | From (Input)    | R <sub>L</sub> = 400Ω, | Units |        |

|------------------|-------------------------------------------------|-----------------|------------------------|-------|--------|

|                  | Falameter                                       | To (Output)     | Min                    | Max   | Offics |

| f <sub>MAX</sub> | Maximum Clock Frequency                         |                 | 15                     |       | MHz    |

| t <sub>PHL</sub> | Propagation Delay Time HIGH-to-LOW Level Output | Clear to Q      |                        | 40    | ns     |

| t <sub>PLH</sub> | Propagation Delay Time LOW-to-HIGH Level Output | Clear to Q      |                        | 25    | ns     |

| t <sub>PHL</sub> | Propagation Delay Time HIGH-to-LOW Level Output | Clock to Q or Q |                        | 40    | ns     |

| t <sub>PLH</sub> | Propagation Delay Time LOW-to-HIGH Level Output | Clock to Q or Q |                        | 25    | ns     |

#### SN5473, SN54LS73A, SN7473, SN74LS73A DUAL J-K FLIP-FLOPS WITH CLEAR

SDLS118 - DECEMBER 1983 - REVISED MARCH 1988

NOTE 1: Voltage values are with respect to network ground terminal.

3